# **IOWA STATE UNIVERSITY Digital Repository**

Graduate Theses and Dissertations

Iowa State University Capstones, Theses and Dissertations

2017

# Accurate Jitter Decomposition in High-Speed Links

Yan Duan Iowa State University

Follow this and additional works at: https://lib.dr.iastate.edu/etd

Part of the <u>Electrical and Electronics Commons</u>

#### Recommended Citation

Duan, Yan, "Accurate Jitter Decomposition in High-Speed Links" (2017). Graduate Theses and Dissertations. 16276. https://lib.dr.iastate.edu/etd/16276

This Dissertation is brought to you for free and open access by the Iowa State University Capstones, Theses and Dissertations at Iowa State University Digital Repository. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Iowa State University Digital Repository. For more information, please contact digirep@iastate.edu.

## Accurate jitter decomposition in high-speed links

by

#### Yan Duan

A dissertation submitted to the graduate faculty in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY

Major: Electrical Engineering

Program of Study Committee:

Degang Chen, Major Professor

Randall L Geiger

Chris Chong-Nuen Chu

Yong Guan

Meng Lu

Iowa State University

Ames, Iowa

2017

Copyright © Yan Duan, 2017. All rights reserved.

# **DEDICATION**

To my family

# TABLE OF CONTENTS

| ACKNOWLEDGMENTS                                             | V  |

|-------------------------------------------------------------|----|

| ABSTRACT                                                    | vi |

| CHAPTER 1 INTRODUCTION                                      | 1  |

| 1.1 Motivation                                              | 2  |

| 1.2 Jitter Basics                                           |    |

| 1.3 Contributions of the Dissertation                       | 9  |

| Reference                                                   | 1. |

| CHAPTER 2 DUTY CYCLE DISTORTION AMPLIFICATION IN            |    |

| HIGH-SPEED DATA CHANNELS                                    | 13 |

| 2.1 Introduction                                            | 13 |

| 2.2 DCD Jitter Amplification Analysis                       | 20 |

| 2.3 Simulation Results                                      | 24 |

| 2.4 Conclusion                                              | 28 |

| Reference                                                   | 29 |

| CHAPTER 3 ACCURATE JITTER DECOMPOSITION IN HIGH-SPEED LINKS | 31 |

| 3.1 Introduction                                            | 31 |

| 3.2 Jitter Modeling                                         | 34 |

| 3.3 Jitter Decomposition Algorithm                          | 38 |

| 3.4 Simulation Results                                      | 42 |

| 3.5 Measurement Results                                     | 46 |

| 3.6 Conclusion                                              | 49 |

| 3.7 Acknowledge                                             | 49 |

| Reference                                                   | 50 |

| CHAPTER 4 A LOW-COST COMPARATOR-BASED METHOD FOR            |    |

| ACCURATE DECOMPOSITION OF DETERMINISTIC JITTER              |    |

| IN HIGH-SPEED LINKS                                         |    |

| 4.1 Introduction                                            |    |

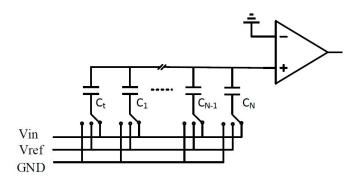

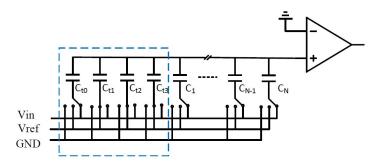

| 4.2 Comparator Based Decomposition Method                   | 57 |

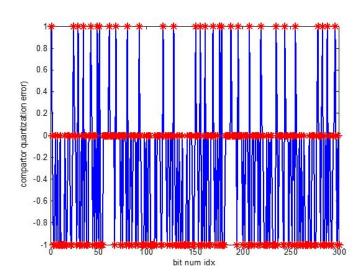

| 4.3 Simulation Results                                      | 71 |

| 4.4 Measurement Results                                     | 76 |

| 4.5 Conclusion                                              | 79 |

| 4.6 Acknowledgment                                          | 80 |

| Reference                                                   | 80 |

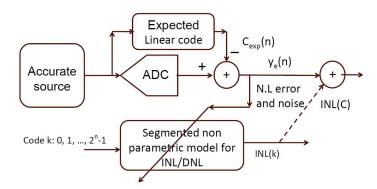

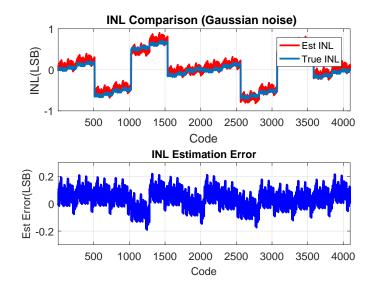

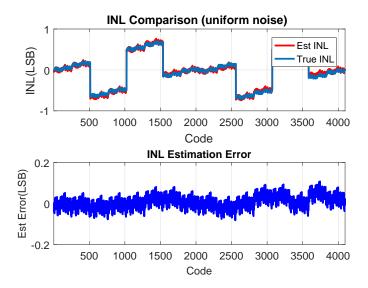

| CHAPTER 5 A LOW-COST DITHERING METHOD FOR IMPROVING ADC | (   |

|---------------------------------------------------------|-----|

| LINEARITY TEST APPLIED IN USMILE ALGORITHM              | 84  |

| 5.1 Introduction                                        | 85  |

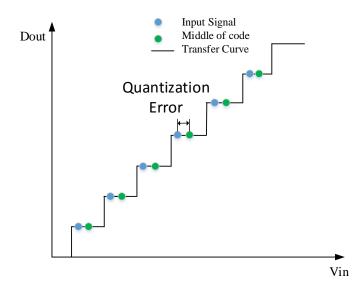

| 5.2 Problem Statement                                   | 87  |

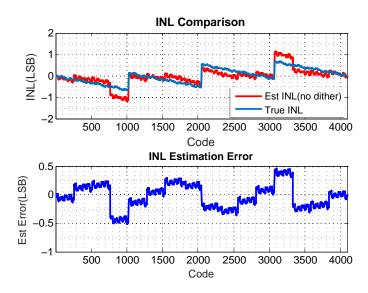

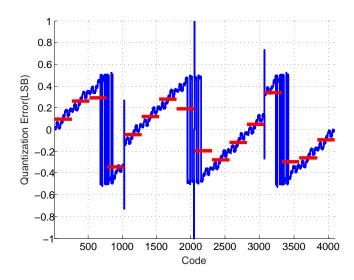

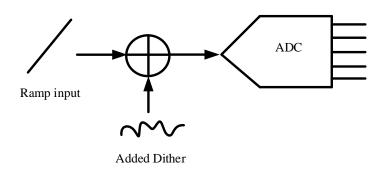

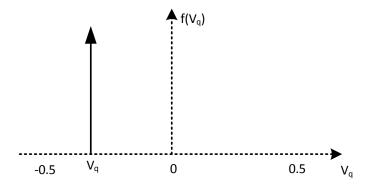

| 5.3 Proposed Dithering Method                           | 92  |

| 5.4 Simulation Results                                  | 102 |

| 5.5 Measurement Results                                 | 104 |

| 5.6 Conclusion                                          | 106 |

| Reference                                               | 107 |

| CHAPTER 6 DISSERTATION CONCLUSION                       | 112 |

| APPENDIX DERIVATION OF EQUATION 5.4                     | 121 |

#### **ACKNOWLEDGMENTS**

This dissertation cannot be completed without support of many people. First of all, I would like to express my deepest gratitude to my advisor Dr. Degang Chen for his valuable guidance, constructive suggestions, and patient encouragement at Iowa State University. Dr. Chen greatly helps me in developing both academic and personal skills.

I would also like to thank my committee members, Dr. Randall L Geiger, Dr. Chris Chong-Nuen Chu, Dr. Yong Guan and Dr. Meng Lu for their valuable e orts and suggestions on my dissertation. Thanks Dr. Jihong Ren, Dr. Wenyi Jin, Dr. Ruth Wei Li in Altera, Dr. Yuming Cao, Mr. Liang Gu in Huawei, Dr. Mike Peng Li in Intel for their technical assistance to my research. Thanks Dr. Yunfeng Li and Ms. Debbie Younkin for reviewing my dissertation and improving my English in the past a few years. I would also like to thank my classmate Dr. Yifei Li for helping me in various aspects during my time at Iowa State University. I would like to thank Rui Zhou and Tao Chen who loved me.

My special thanks go to my beloved family members. My parents, Yubing Zhou, my sisters, and my lovely nephews and niece gave me a lot of support in my study and my live. I do not think I can finish this without their endless encouragement and support.

#### **ABSTRACT**

In a high-speed digital communication system, jitter performance plays a crucial role in Bit-Error Rate (BER). It is important to accurately derive each type of jitter as well as total jitter (TJ) and to identify the root causes of jitter by jitter decomposition. In this work, we propose new jitter decomposition techniques in high-speed links testing. The background of jitter decomposition is described in chapter 1.

In chapter 2, duty cycle distortion jitter amplification is introduced. As channel loss results in both ISI and jitter amplification, DCD amplification is a big concern in high-speed links. The derivation of a formula of DCD amplification for data channels is included and the calculation result matches the time-domain simulation in the system.

Chapter 3 provides an accurate jitter decomposition algorithm using Least Squares (LS) which simultaneously separates ISI, RJ, and PJ. A new time domain ISI model is proposed, which is faster and more accurate than the conventional ISI model. This algorithm obtains the estimated individual jitter component value with fine accuracy by using less samples of total jitter data compared with conventional methods. The simulation and measurement show the accuracy and efficiency of this algorithm with less data samples.

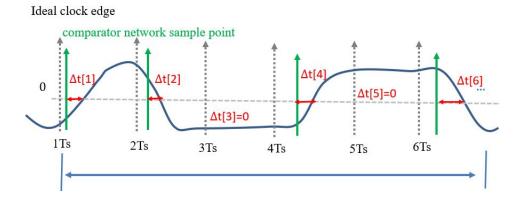

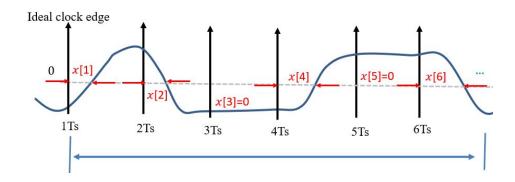

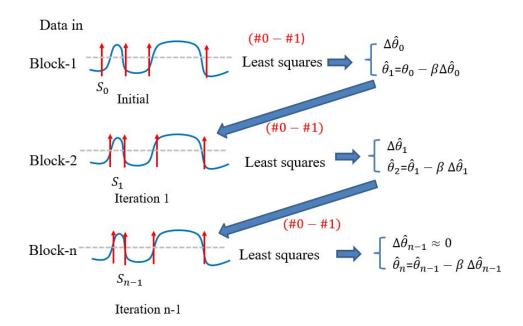

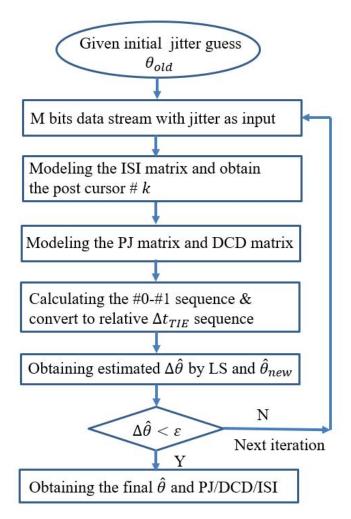

In chapter 4, a low-cost comparator-based jitter decomposition algorithm is proposed. Instead of using TIE jitter sequence to decompose, it uses a low cost and simple comparator network to identify the deviation of current sampling positions from the ideal sampling positions to represent the TIE. It simultaneously separates ISI, DCD, and PJ and can achieve similar accuracy compared to the instrument test. Both the simulation and measurement show the decomposition algorithm with great accuracy and efficiency.

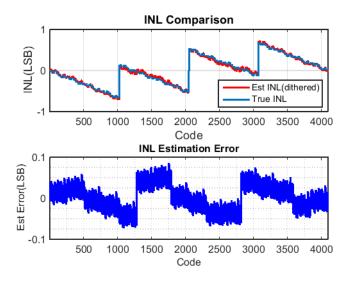

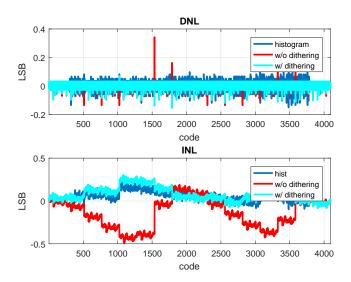

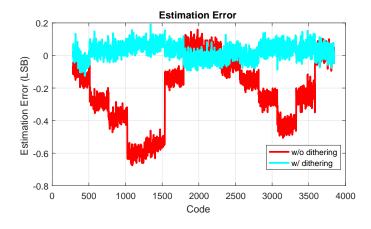

In chapter 5, a low cost and simple dithering method to improve the test of linearity of analog-to-digital converter (ADC) is proposed. This method exhibits an improve ment and enhancement for the ultrafast segmented model identification of linearity error (uSMILE) algorithm which reduces 99% of the test time compared to the conventional method. In this study, we proposed three types of distribution dithering methods adding to the ramp input signal to reduce the estimation error when uSMILE was applied in low resolution ADCs. The fix pattern distribution was proved as the most efficient and cost-effective method by comparing with the Gaussian, uniform, and fix-pattern distributions. Both the simulation results and hardware measurement indicate that the estimation error can be significantly reduced in 12-bit SAR ADC with effective dithering.

#### CHAPTER 1. INTRODUCTION

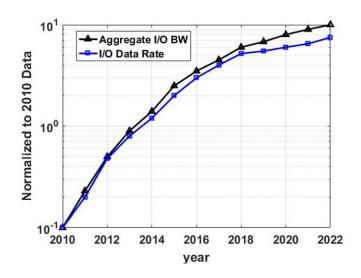

The data processing capabilities of integrated circuits increased greatly due to scaling of integrated circuit technology in the past decade. However, digital data communication has become one of the dominant reasons which cause bottlenecks in these systems. To overcome these bottlenecks, more sophisticated high-speed link circuits have replaced those simple input/output (I/O) drivers integrated in these chips. The aggressive scaling of I/O bandwidth demands double every two to three years on average [1] as shown in Figure 1.1. However, the I/O performance is limited by electrical channel bandwidth limits.

Figure 1.1 I/O data rate and bandwidth requirement

Meanwhile, as the data rate increases, the inter symbol interference (ISI) becomes

severe due to the bandwidth limitation. Jitter and noise, generated inevitably in the transmitter, channel and receiver, impact the performance of the system.

#### 1.1 Motivation

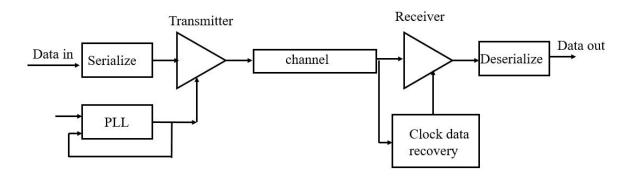

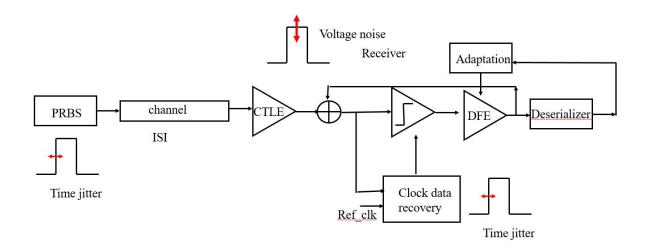

A typical high-speed link composes of the three main blocks, transmitter, channel and receiver [2-3] as shown in Figure 1.2.

Figure 1.2 I/O High-speed link block diagram

The transmitter (TX) buffer is triggered by phase-locked loop (PLL). A high-frequency transmit clock is generated by PLL. The channel is the whole path from the output of the transmitter to the input and then to the receiver. The channel includes any printed circuit board (PCB) trace and coaxial cables that are used to connect the packages together. Signal degradation is caused by the channel due to a low pass characteristic. It limits data throughput by introducing noise and signal distortions, which both lead to ISI jitter. The transmitted data voltage is sampled by the receiver (RX). A clock and data recovery (CDR) circuit on the receiver usually incorporates a PLL. Some additional circuits are needed to synchronize the receiver with the incoming data stream.

As a synchronization circuit, the RX-PLL has to cope with input jitter, and it pro-

vides certain robustness against timing variations. Timing variations will not be tracked correctly by the PLL if jitter exceeds critical amplitude. And hence, it leads to erroneous signal recovery of the received data, which the whole process will affect the bit-error-rate (BER). Thus, it is important to look carefully into the jitter and noise sources in order to determine the maximum data rate of the link with the guaranteed BER target in high-speed links. Jitter decomposition analysis involves the use of histogram or statistical analysis, frequency analysis, time domain methods. In this dissertation, several jitter decomposition analysis methods are developed and analyzed. They are also applied to practical simulations and measurement cases. This chapter will present some background information about jitter in high-speed links before starting jitter analysis methods.

#### 1.2 Jitter Basics

#### 1.2.1 Jitter Definition

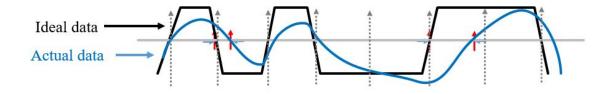

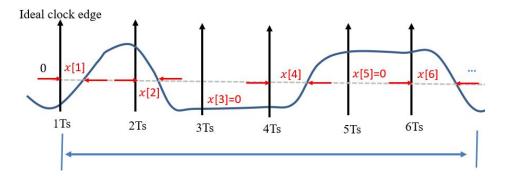

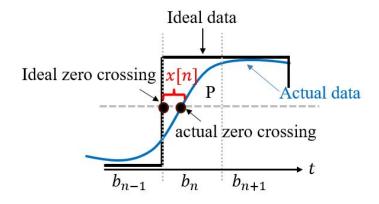

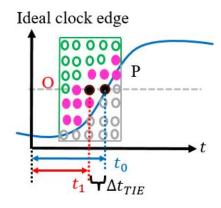

Jitter is defined as the variation of ideal edges and actual edges in time domain both for clock and data. Figure 1.3 shows the definition of jitter. TIE jitter is the actual deviation from the ideal clock period over all clock periods

Figure 1.3 I/O High-speed link block diagram

#### 1.2.2 Jitter in High-Speed Link

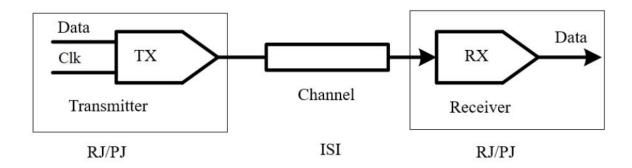

Since timing uncertainty is the major reason for erroneous data recovery, a robust receiver architecture is one of the most challenging design criteria. Figure 1.4 shows various jitter sources contributing to the overall jitter in a high-speed link.

Figure 1.4 Different jitter within a typical serial link

As shown in Figure 1.4, there are two important sources of noise and jitter on the TX: the TX clock jitter and the TX power supply noise [2]. Any phase noise on the transmit clock will translate into timing jitter and the TX power supply noise is induced by the asynchronous current switching of all the I/Os, which may couple into the transmitted signal [2]. It can be lowered by careful layout and decoupling capacitors. Meanwhile, the RX also causes RX sampling jitter and RX power supply noise, which is similar to the TX end. However, the received signal is much more sensitive to the noise and jitter since the detected signal has a smaller voltage amplitude. The channel is the final element of a communication link that generates noise and jitter as illustrated in Figure 1.4. The channels limited bandwidth produces ISI, which varies the transition edge slope, inducing data-dependent jitter (DDJ)[2-3].

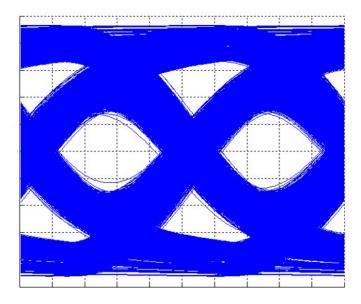

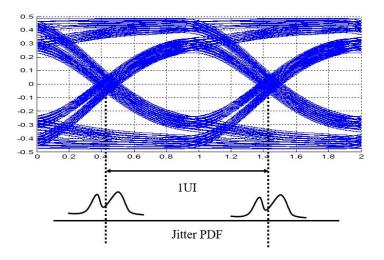

The eye diagram is a common way to highlight the problem of signal recovery and presence of jitter as depicted in Figure 1.5. Researchers use eye diagrams to quantify

Figure 1.5 The effect of non idealities on an eye diagram

noise margin degradation. An ideal eye diagram shows a perfect rectangle. However, jitter and voltage noise cause the transition slope to be slower, thereby closing the eye opening. Jitter especially degrades system performance by causing a large horizontal eye closure voltage noise causes a large vertical eye closure.

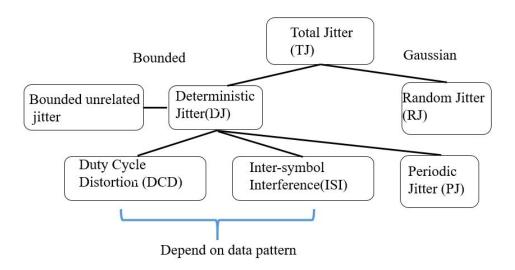

An observed total jitter (TJ) distribution includes different components [2-3] shown in the scheme in Figure 1.6. It can basically be decomposed into a bounded deterministic jitter (DJ) and an unbounded random jitter (RJ). RJ is usually considered as Gaussian, unbounded probability behavior. It is observed at both distribution tails, extending them toward infinity. DJ can be of arbitrary shape and is expressed by various subcomponents in order to distinguish various root causes. DJ is further divided into periodic (PJ), bounded uncorrelated (BUJ), and data-dependent jitter (DDJ). DDJ is related to the transmitted data pattern. DDJ consists of duty-cycle distortion (DCD) and ISI. DCD is caused by a difference in the pulse width between logical high and low levels which is caused by voltage offsets or different rise and fall times at signal transitions. BUJ is always considered bounded because of the limited coupling strength.

Figure 1.6 Jitter components classification

## 1.2.3 Jitter Decomposition Methods

With the increasing data rates in the high-speed communication system, there is a significant challenge in balancing test cost and quality to test high-speed interfaces. Currently available jitter measurement techniques require expensive and high precision measurement instruments, including the use of high-speed sampling scopes, time interval analyzers (TIAs) and bit error rate testers (BERTs) [2-3].

Different off-chip decomposition approaches have been developed in the past. Generally there are three popular category approaches to decompose jitter: 1) the ones based on histogram or statistical methods; 2) the ones with frequency-domain based analysis; and 3) the ones with time-domain based analysis relying on jitter measurements carried out in real-time. In the following sections these three analysis domains will be explained in more detail in order to give a comprehensive overview to the state-of-the-art in the topic.

Figure 1.7 Histogram based method model

Figure 1.8 RJ and DJ components of a jitter PDF.

#### 1.2.3.1 Histogram Based Analysis

Probability distributions of collected jitter values are used to estimate jitter influence in histogram or statistical domain-based methods. A jitter distribution in an eye diagram is obtained from the horizontal cross section at a desired signal level in Figure 1.7.

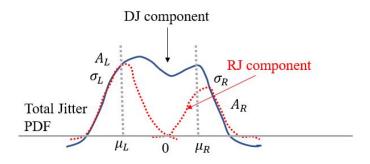

The collected distribution corresponds to probability density function (PDF) of jitter samples. Common model assumptions are the popular Gaussian tail model [2] which has the following features: 1) Jitter is a stationary random process. 2) The measured TJ distribution can be separated into two components, RJ and DJ. 3) RJ is observed at

the outer tails of a TJ distribution, and follows an unbounded Gaussian by its mean, standard deviation and amplitude A. 4) DJ follows a finite, bounded distribution which is shown in Figure 1.8. Three model parameters  $\mu$ ,  $\sigma$  and A for both tails should be identified by analysis methods in order to correctly extrapolate a measured distribution. For this purpose, some researchers also refer these methods as tail fitting algorithms or jitter decomposition methods. Various methods were developed to decompose the RJ and DJ components with tail fitting algorithms [4-8]. However, there are two obvious drawbacks in tail fitting approaches. First, it needs to identify the tail part of the distribution before starting the optimization. The identification algorithm with conservative parameters works suboptimal for many of the distribution shapes. Secondly, the tail fitting algorithm is very complex and requires many samples.

#### 1.2.3.2 Time-Domain Based Analysis

The time-domain based jitter analysis [8-10] rely on jitter measurements carried out in real-time. This is only possible for dedicated real-time measurement systems, such as high speed sampling scopes or TIAs. Some methods have been proposed in the past. Dou and Abraham [9-10] introduced correlation analysis. Unfortunately, this method still lacks a relation between extracted DJ subcomponents and the TJ. It is unable to apply to arbitrary jitter distributions and requires a large amount of test samples which is not a practical simulation application.

#### 1.2.3.3 Frequency-Domain Based Analysis

Some research proposed the jitter decomposition based on the Fourier transform (FT) [11-13]. In frequency-domain analysis, the power spectral density (PSD) is used to represent the jitter spectrum by applying averaging techniques. Peaks in the spectrum can be interpreted as PJ or DDJ and the average noise floor denotes the power of RJ. In [9-10] four spectral regions of the jitter transfer function are defined to allow for

BER analysis. The approach is restricted to Gaussian RJ combined with PJ. Although jitter measurements using external instruments can be performed in the lab for characterization, instruments are unable to lend themselves to fast parallel testing of devices with a large number of high-speed interfaces due to their hardware complexity, cost and scalability limitations.

#### 1.3 Contributions of the Dissertation

In this dissertation, we will propose new jitter decomposition techniques that address the mentioned challenges above in high-speed links testing. The dissertation is organized with four major chapters, which each chapter presents and solves some technical issues in the area of jitter decomposition.

In chapter 2, duty cycle distortion (DCD) jitter amplification will be introduced. As channel loss results in both ISI and jitter amplification, DCD amplification is a big concern in high-speed links. An overview of the statistical jitter modeling and jitter amplification of clock channel will be briefly discussed. The derivation of a formula of DCD amplification for data channels will be included. The calculation result matches the time-domain simulation in the system.

Chapter 3 will provide an accurate jitter decomposition algorithm using Least Squares (LS) which simultaneously separates ISI, RJ, and PJ (called TIE-based method in the dissertation). Jitter basic information with PJ, DCD and RJ will be introduced. A new time-domain ISI model will be used in the algorithm and it is faster and more accurate than the conventional ISI model. This algorithm will obtain estimated individual jitter component values with fine accuracy by using less samples of total jitter data compared to conventional methods.

In chapter 4, a low-cost comparator based jitter decomposition algorithm will be presented. Instead of using TIE jitter sequence to decompose, it will use a low cost and

simple comparator network to identify the deviation of current sampling positions from the ideal sampling positions to represent the TIE (called comparator-based method in this thesis). It can simultaneously separate ISI, DCD, and PJ and this algorithm achieves similar accuracy compared to the instrument test.

In chapter 5, a low cost and simple dithering method to improve the test of linearity of analog-to-digital converter (ADC) will be discussed. This method is an improvement and enhancement for the ultrafast segmented model identification of linearity error (uSMILE) algorithm, which reduces 99% of the test time compared to the conventional method. Since uSMILE produces large estimation errors in low resolution ADCs (10-12 bits) when the input is a ramp signal, in which the quantization noise of ADC becomes a dominant part in the total noise. We will compare with three types of distribution dithering methods to add the ramp input signal to reduce the estimation errors when uSMILE is applied in low resolution ADCs.

In chapter 6 concludes the whole dissertation.

#### REFERENCE

- [1] International Technology Roadmap for Semiconductors, 2011 edition, [Online].

Available: http://public.itrs.net

- [2] M. P. Li, "Jitter, noise and signal integrity at high-speed," Prentice Hall Pearson Education, 2007

- [3] D.Oh and X.Yuan, "High speed signaling: jitter modeling analysis, and budgeting," Prentice Hall Pearson Education, 2011, Chapter 3, pp.44-64

- [4] J.-L. Huang, "A Random Jitter Extraction Technique in the Presence of Sinusoidal Jitter," IEEE Asian Test Symp. (ATS06), pp. 318326, Nov. 2006.

- [6] R. Stephens, "Separation of Random and Deterministic Components of Jitter," U.S. Patent 7149638, Dec. 12, 2006.

- [6] R. Stephens, "Separation of a Random Component of Jitter and a Deterministic Component of Jitter," U.S. Patent 7 191080, Mar. 13, 2007.

- [7] S. Wisetphanichkij and K. Dejhan, "Jitter Decomposition by Derivatived Gaussian Wavelet Transform," IEEE Int. Symp. Communication and Information Technology (ISCIT04),vol. 2, pp. 11601165, Oct. 2004.

- [8] F. Nan, Y. Wang, F. Li, W. Yang, and X. Ma, "A Better Method than Tail-fitting Algorithm for Jitter Separation Based on Gaussian Mixture Model," J. of Electronic Testing: Theory and Applications, vol. 25, no. 6, pp. 337342, Dec. 2009.

- [9] Q. Dou and J. Abraham, "Jitter Decomposition by Time Lag Correlation," IEEE Int. Symp. Quality Electronic Design (ISQED06), Mar. 2006

- [10] "Physical Layer Performance: Testing the Bit Error Ratio (BER)," Technical Article, Maxim Inc., Sep. 2004

- [11] H. Pang, J. Zhu, and W. Huang, "Jitter decomposition by fast Fourier transform and time lag correlation," in IEEE Int. Conf. Communications, Circuits and Systems ICCCAS, Jul. 2009, pp. 365368.

- [12] T. Yamaguchi, H. Hou, K. Takayama, D. Armstrong, M. Ishida et al., "An FFT-based jitter separation method for high-frequency jitter testing with a 10x reduction in test time," IEEE Int. Test Conf. (ITC07), pp. 18, Oct. 2007.

# CHAPTER 2. DUTY CYCLE DISTORTION AMPLIFICATION IN HIGH-SPEED DATA CHANNELS

Clock channel jitter amplification scales exponentially with channel loss and is the worst for duty cycle distortion (DCD) due to its high frequency nature. As the channel loss results in both inter-symbol interference (ISI) and jitter amplification, the DCD amplification in data channel is not as well understood and clearly quantified as clock channel DCD amplification. This chapter presents a general formula to calculate the data channel DCD amplification based on peak distortion analysis and statistical jitter modeling methodology. The presented methodology is validated by time-domain simulation on different lossy channels.

#### 2.1 Introduction

As data rates continue to climb at an ever-increasing rate, jitter and noise in high-speed links have become a performance bottleneck in addition to signal integrity issues such as inter-symbol interference (ISI) and crosstalk. ISI has three main causes: 1) bandwidth limitation of transmission medium; 2) nonlinear phase response of the transmission medium; 3) reflection. Random jitter (RJ) is commonly modeled by the Gaussian distribution function. Common sources of RJ include shot noise and thermal noise. Duty-cycle distortion (DCD) is caused different rise and fall times at signal transitions and device mismatch in signal path. Electromagnetic interference from other devices or the system can also induce current on signal wires and affect the signal voltage biasing and reference

voltage.

Jitter exists in both receivers and transmitters in high-speed links. Compared to receiver jitter, transmitter jitter is more detrimental as transmitter jitter modulates transmitted pulse width directly. The amount of jitter is modulated by channel dispersion as signals propagate in the system. It has been shown that clock channel jitter amplification scales exponentially with channel loss even when the channel is linear, passive, and noiseless [1-4]. The mechanism of jitter amplification is discussed in terms of channel impulse/step response in [2-4]. In particular, DCD and RJ amplifications in clock signals are shown to scale uniquely with channel loss [2], indicating that loss is responsible for the effect. It is the worst amplification for duty-cycle distortion (DCD) as DCD has the highest jitter frequency contents [1-4]. DCD amplification presents a great limitation on clock forwarding architecture at high data rates. In modern high-speed serial links shown in Figure 2.1, the clock is typically embedded in high-speed data stream, and a clock and data recovery (CDR) circuit are used to recover both the data and clock. As channel loss results in both ISI and jitter amplification, DCD amplification in data channels is not as well understood and quantified.

Figure 2.1 Typical high-speed link

Among the typical mixed-signal equalization techniques such as transmitter finite impulse response (FIR) equalizer, analog continuous time linear equalizer (CTLE), and decision feedback equalizer (DFE), only CTLE can reduce the jitter amplification effect due to its continuous time nature. Due to the limitation of CTLE gain-bandwidth product, DFE is typically heavily-relied upon for high-loss channels. Therefore, it is important that the impact of transmitter jitter, especially transmitter DCD, is accurately estimated and accounted for timing budget for high-speed serial links.

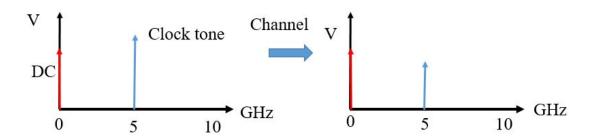

DCD amplification in clock channels was well explained in frequency domain in [4]. A clock signal with DCD consists of two major frequency components, a DC component and the clock tone itself. The lossy passive channel attenuates the high frequency clock tone much more than the DC component and thus it results in DCD amplification shown in Figure 2.2.

Figure 2.2 Frequency analysis for jitter amplification in clock pattern

In [2-3], a general statistical formulation was developed to model transmitter jitter amplification in clock channels based on channel step responses. Clock jitter was first converted into voltage noise and then converted back to timing jitter using the slope of the output clock signal. All the analysis and data in [1-4] show that clock channel DCD amplification scales exponentially with the channel loss.

The analysis in [1-4] was limited to DCD amplification in clock channels. The pe-

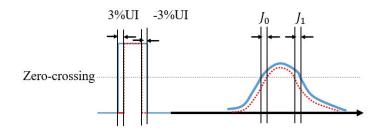

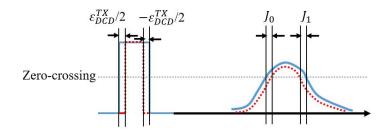

riodicity of the 1010 clock pattern eliminates ISI jitter therefore jitter at the channel output is entirely induced by input jitter. For clock channels, jitter amplification factor is defined as the ratio of output jitter over input jitter. Since the channel loss results in both ISI jitter and jitter amplification, this definition of jitter amplification is no longer applicable to data channels. In contrast, what really matters in data channels is the additional margin loss due to transmitter jitter. DCD amplification in data channel is defined as the ratio of additional margin loss and input DCD. For example, if 3%UI DCD results in 6%UI additional margin loss (J0 J1) at the channel output compared with zero DCD case, the DCD amplification factor is 2, shown in Figure 2.3. It is important in balancing timing budget in high-speed serial links to insight how data channel DCD amplification scales with channel loss, especially for high data rate applications on high-loss channels.

Figure 2.3 DCD amplification definition in data channel

This chapter extends the DCD amplification analysis for clock channels in [3] to data channels and presents a general formula to calculate the factor of data channel DCD amplification based on peak distortion analysis and statistical jitter modeling methodology. The rest of chapter is organized as follows. Section II describes DCD jitter amplification analysis based on a statistical modeling methodology for data channels and clock channels. Section III validates the methodology with time-domain simulation results. Section V summarizes this chapter.

#### 2.1.1 Jitter Amplification Background

This section first reviews channel single bit response, the statistical transmitter jitter modeling methodology presented in [3, 5] and peak distortion analysis [6-7] as they are the basis of this work. Then a general formula for data channel DCD amplification is derived.

#### 2.1.1.1 Channel Single Bit Response

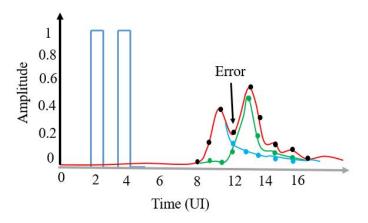

In a high-speed link, the channel has low-pass filter characteristic due to the skineffect and dielectric loss. This means an ideal narrow pulse at the input of the channel will be significantly attenuated and much wider at the output of the channel. It occupies the pre-cursor  $(h_{-1}, h_{-2}, \cdots)$  and post cursor samples  $(h1, h2, \cdots)$ . Other than that, the first pre-cursor  $(h_{-1})$  and post-cursor  $(h_1)$  samples are very large due to the pulse dispersion from low-pass filtering,  $h_0$  is the main-cursor. Both effects would make it very difficult to correctly detect the bits that are transmitted in a sequence.

Figure 2.4 ISI cause bit error

For example, a received sample as shown in Figure 2.4 that corresponds to bit zero drops to only 0.4 due to interference from the previous bit by 0.2 and the next bit by 0.1 in a one zero-one pattern sent from the transmitter. As a result, this bit is received

as an error.

This inter-symbol interference (ISI) effect is deterministic since it is repeated by transmitting the same data pattern. It is obvious that this effect becomes severe as the width of the transmitted bit decreases. As such, ISI is clearly one of the most significant effects that limit the achievable data rates in high-speed backplane links.

#### 2.1.2 General Statistical System Jitter Modeling

Assuming linear time invariance (LTI) throughout the rest of this chapter, the channel output signal y(t) without transmitter and receiver jitter can be expressed in terms of the superposition of progressively delayed channel step responses

$$y[n] = \sum_{k} (d_k - d_{k-1})s(t - kT)$$

(2.1)

where s(t) is the step response of the channel, k is the input symbol index, T is the symbol time, and  $d_k$  is the transmit symbol at time k. The step responses can be derived from the S-parameter of the passive channel.

With the transmitter jitter,  $\varepsilon_k^{TX}$ , the output of the channel becomes

$$y[n] = \sum_{k} (d_k - d_{k-1})s(t + \varepsilon_k^{TX} - kT)$$

(2.2)

After sampling at t = mT, the output  $y_m$  can be expressed in terms of the superposition of progressively delayed channel step responses as follows [3, 5]:

$$y_m = \sum_{k} (d_k - d_{k-1}) s(\varepsilon_k^{TX} + (m-k)T)$$

(2.3)

For small transmitter jitter  $\varepsilon_k^{TX}$ , following the method in [9], the channel output signal can be decomposed into the ideal signal and the effective voltage noise  $n_m^{TX}$  induced by  $\varepsilon_k^{TX}$  using Taylor series expansion as follows:

$$y_m(t) = \sum_{k} (d_k - d_{k-1})s((m-k)T) + \sum_{k} ((d_k - d_{k-1})\varepsilon_k^{TX} h_{m-k})$$

(2.4)

where  $h_m$  is the data rate sampled impulse response of the channel. The effective voltage noise  $n_m^{TX}$  due to transmitter jitter at the input of the sampler is:

$$n_m^{TX} = \sum_{k} ((d_k - d_{k-1})\varepsilon_k^{TX} h_{m-k})$$

(2.5)

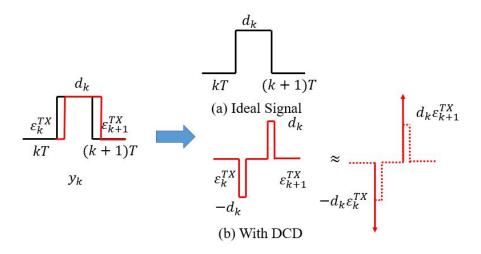

Based on equation 2.4, data with small DCD  $\varepsilon_k^{TX}$  can be explained as the superposition of a noiseless data stream  $d_k$  in Figure 2.5 and two noise pulses  $\varepsilon_k^{TX}$  and  $\varepsilon_{k+1}^{TX}$  [8]. Since the DCD is much narrower than the impulse response of the channel filter and the reference symbol pulse, we can approximate them with delta functions as described in [8] when the noise data passes through the channel filter.

Figure 2.5 DCD converts to noise

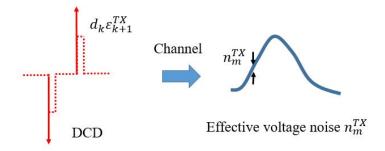

A symbol transmitted with DCD is converted into a symbol with no jitter Figure 2.5(a) and a noise term where the width values of the noise symbols Figure 2.5(b) are equal to  $\varepsilon_k^{TX}$  and  $\varepsilon_{k+1}^{TX}$ . Therefore, the transmitter jitter can be mapped into effective noise  $n_m^{TX}$  shown Figure 2.6.

Figure 2.6 Data with DCD decomposition

# 2.2 DCD Jitter Amplification Analysis

This section described a general formula for data channel DCD amplification. The first step was to convert the receiver effective noise into zero-crossing jitter. The second step was to obtain the DCD amplification by using the worst-case pattern based on peak-distortion analysis. Meanwhile, we obtained the DCD amplification for clock pattern.

#### 2.2.1 Converting Effective Noise to Jitter

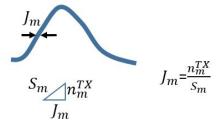

Equation 2.5 shows that transmitter jitter on any one edge affects the channel output waveform in the vicinity of neighboring edges in a way determined by the channel impulse response and data pattern. The higher the channel loss is, the longer the channel impulse response and hence the larger the jitter accumulation will be. The effective voltage noise  $n_m^{TX}$  at the zero crossings can be translated back to timing jitter using the slope of the channel output waveform [3]  $S_m$  shown in Figure 2.7.

In Figure 2.7, jitter at zero-crossing which is converted by the effective noise  $n_m^{TX}$ , Jm is the timing jitter at mth zero-crossing. The jitter at the zero crossing is given by

$$J_M = n_m^{TX} / S_M \tag{2.6}$$

For any data pattern, the slope of the channel output at the zero crossing is given by

$$S_M = \sum_{k} ((d_k - d_{k-1})h_{m-k})$$

(2.7)

Figure 2.7 Converting the effective noise to jitter at zero-crossing

Mapping the effective voltage noise back to timing jitter, we obtained

$$J_M = \sum_{k} ((d_k - d_{k-1})\varepsilon_k^{TX} h_{m-k}) / \sum_{k} ((d_k - d_{k-1})h_{m-k})$$

(2.8)

#### 2.2.2 DCD Amplification of Data Channel

Note that both the slope and the effective voltage noise are various for different data patterns. The definition of jitter amplification as the ratio of output jitter over input jitter is no longer valid. In contrast, as mentioned earlier, what matters is the additional margin loss due to DCD for data channel. For a random bit pattern, peak distortion analysis is widely used to estimate worst-case eye opening [6-7]. The difference between the worst-case eye opening with and without transmitter DCD is a good estimation of the additional margin loss due to transmitter DCD.

To determine the worst-case voltage or timing margin, the worst-case received eye shape is extracted along with the peak sampling boundary. Since sources such as ISI have truncated distributions, the associated worst-case magnitudes can be direct from the single bit response of the system [9]. Based on peak-distortion analysis, the worst-case pattern that results in the worst-case eye opening can be easily extracted for a given channel single bit response (SBR). Given a SBR, the largest undershoot can be estimated by choosing the signs of the other data bits that result in negative (positive) ISIs for the case where current data bit is 1 (-1) [6-7]. Given the symbol-spaced single bit response,

pulse cursor coefficient is given by

$$h = [\cdots, h_{-2}, h_{-1}, h_0, h_1, h_2, \cdots]$$

(2.9)

Figure 2.8 Single bit and worst case pattern

Flip pulse matrix about cursor  $h_0$  and the bits are inverted sign of the pulse ISI, the worst-case pattern can be obtained by

$$\overrightarrow{d}_{worst}^T = [\cdots, -sign(h_2), -sign(h_1), 1, -sign(h_{-1}), -sign(h_{-2}), -sign(h_{-2}), \cdots]$$

$$(2.10)$$

For a smooth lossy channel where all ISIs are positive, its worst-case pattern is simply a single bit shown in Figure 2.8. For this worst-case data pattern, if the transmitter jitter at rising edge is  $(\varepsilon_0^{TX})$  and at falling edge is  $\varepsilon_1^{TX}$ , the calculated jitter at the rising $(J_0)$  and falling edges  $(J_1)$  of the single bit according to equation 2.8 after channel is:

$$J_0 = \frac{h_0 \varepsilon_0^{TX} - h_{-1} \varepsilon_1^{TX}}{h_0 - h_{-1}} \tag{2.11}$$

$$J_1 = \frac{-h_0 \varepsilon_1^{TX} + h_1 \varepsilon_0^{TX}}{h_0 - h_1} \tag{2.12}$$

The additional margin loss due to jitter is the sum of  $J_0$  and  $J_1$  which is given by

margin loss =

$$\frac{h_0^2 - h_1 h_{-1}}{(h_0 - h_1)(h - h_{-1})} (\varepsilon_0^{TX} - \varepsilon_1^{TX})$$

(2.13)

For sinusoidal jitter, margin loss is the biggest when  $\varepsilon_0^{TX} - \varepsilon_1^{TX}$  is at the maximum value. The higher the sinusoidal jitter frequency is, the bigger  $\varepsilon_0^{TX} - \varepsilon_1^{TX}$  is for the same sinusoidal jitter magnitude, therefore the higher the margin loss.

DCD is the highest frequency sinusoidal jitter. For DCD,  $\varepsilon_0^{TX} = -\varepsilon_1^{TX} = \varepsilon_{DCD}^{TX}/2$ , where  $\varepsilon_{DCD}^{TX}$  is peak-to-peak transmitter DCD. From (13), the DCD amplification factor defined as additional margin loss over transmitter DCD is given by

$$A_{DCD} = \left(\frac{h_0 + h_{-1}}{h_0 - h_{-1}} + \frac{h_0 + h_1}{h_0 - h_1}\right)/2 \tag{2.14}$$

Equation 2.14 shows that the DCD impact on margin loss is amplified when we have positive  $h_{-1}$  and  $h_1$ , which is the case for lossy channels. The higher the loss is, the bigger  $h_1$  and  $h_{-1}$  are and the bigger the amplification factor is. Therefore, data channel DCD amplification increases with channel loss.

#### 2.2.3 DCD Jitter Amplification of Clock channel

Clock channels can be considered as a data channel with a clock pattern:  $\overrightarrow{d}^T = [\cdots, -1, +1, -1, \cdots]$ , taking  $\overrightarrow{d}^T$  into equation 2.8 we have [3]

$$J_{M} = \frac{\sum_{k} h_{m-k} \varepsilon_{DCD}^{TX} / 2}{\sum_{k} (-1)^{k} h_{m-k}}$$

(2.15)

$$A_{DCD}^{CLK} = \frac{\sum_{k} h_{m-k}}{\sum_{k} (-1)^{k} h_{m-k}}$$

(2.16)

In contrast to the fact that equation 2.14 which only depends on  $h_1$  and  $h_{-1}$ , equation 2.16 shows that clock channel DCD amplification depends on all terms in the channel impulse response therefore it could be much more severe than data channel DCD amplification for high loss channels.

Alternatively, the difference between clock channel DCD amplification and data channel DCD amplification can be explained from jitter frequency point of view. As shown in

[1-4], for clock channel, DCD is the highest frequency jitter which results in the biggest jitter amplification while random jitter with wide spectrum shows much less jitter amplification. The DCD amplification of clock pattern in frequency-domain is

$$F_{DCD} = \left(\frac{H(2w_0)}{H(w)} + \frac{H(0)}{H(-w_0)}\right)/2 \tag{2.17}$$

where  $H(\omega)$  is the transfer function of channel. When the impedance mismatch in the channel is negligible,  $H(\omega)$  is the channel forward S-parameter.  $\omega_0$  is the fundamental frequency of clock signal. In a lossy channel,  $H(\omega)$  decays exponentially with frequency.  $H(\omega-\omega_0)$  is attenuated less than  $H(\omega_0)$ , producing a gain in the output that leads to jitter amplification. From equation 2.17, it shows that DCD amplification is caused by the attenuation difference between the DC component introduced by DCD and the fundamental in lossy channels. Different from clock channel DCD, data channel DCD is being modulated by a random data pattern. Let  $\varepsilon$  be a random sequence of 0s and 1s, where 0 means no edge transition and 1 means edge transition. The data channel DCD sequence can be modeled as the point-wise multiplication of the DCD sequence with the random sequence  $\varepsilon$ . This results in convolution in frequency domain. The random sequence  $\varepsilon$  has wide frequency content. Therefore, intuitive data channel DCD should result in less jitter amplification than clock channel DCD.

#### 2.3 Simulation Results

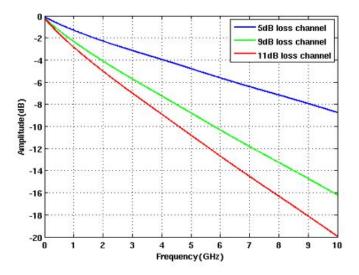

To validate the theory, three channels with different amount of loss were used in time-domain simulation. They have 5dB, 9dB and 11dB insertion losses at 5Gzh, respectively as shown in Figure 2.9 The time-domain test bench was constructed in the Simulink environment. The simulation time step was swept to make sure the time step is fine enough to simulate small jitters. All simulations are done at 10Gbps. These channels have eye openings at 10Gbps without equalization.

Figure 2.9 Channels under consideration

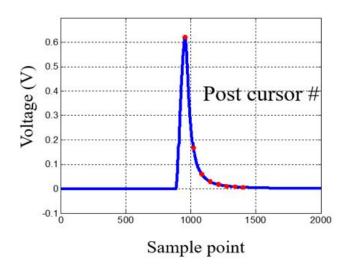

Figure 2.10 Single bit response to extract the worst-case patternn

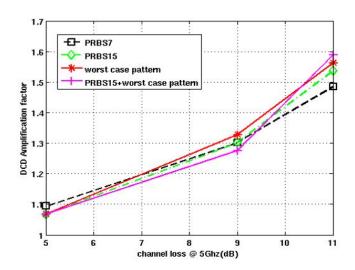

The single bit responses were first simulated for the worst-case pattern extraction, shown in Figure 2.10. Different data patterns, including PRBS7, PRBS15, worst-case pattern and PRBS15 combined with worst-case pattern were used to simulate DCD amplification. For PRBS7 and PRBS15 patterns, at least two full cycles of PRBS pattern length were simulated. The simulation results are shown in Figure 2.11. These simulations

tions were done with  $3\%\mathrm{UI}$  DCD injection.

Figure 2.11 DCD amplification for different data patterns

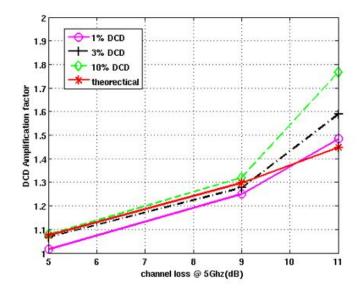

Figure 2.12 Comparison of DCD amplification for different amount of DCD

All data patterns have similar DCD amplification factors. This confirms our intuition that worst-case data pattern can be used to estimate DCD amplification for random data

patterns. Note that the worst-case pattern is much shorter to simulate. As expected, the amplification factor increases as channel loss increases, close to 1.1 for the 5dB low loss channel and up to 1.6 for the 11dB high loss channel. For the 11dB high loss channel, 3% transmitter DCD resulted in 4.8%UI margin loss.

Different amount of DCD signals are injected to show the impact of DCD magnitude on DCD amplification. Figure 2.12 shows DCD amplification factors for different channel losses with 1%, 3%, and 10%UI DCD injection. For the 11dB loss channel, 10%UI DCD results in more than 17%UI margin loss and the largest amplification factor. This again shows the importance of tightening the transmitter DCD budget. The theoretical calculation based on equation 2.8 is also shown in Figure 2.11. It matches well with the time-domain simulation for small DCD as equation 2.8 is based on Taylor series expansion and only holds for small transmitter jitter.

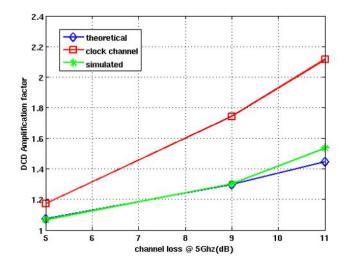

Figure 2.13 Comparison of DCD amplification for different cases

Figure 2.13 overlays the DCD amplification curves for the clock pattern, the worst-case pattern and the theoretical calculation based on equation 2.8. As expected, data channel DCD amplification is smaller than clock channel DCD amplification. Clock channel DCD amplification scales faster with channel loss. For the 5dB low loss channel,

DCD amplification factors for both data and clock channels are close to 1. For the 11dB loss channel, DCD amplification factors for clock and data channels are 2.2 and 1.6, respectively.

# 2.4 Conclusion

This chapter investigates transmitter DCD amplification in data channels and its impact on link margin. Data channel DCD amplification is defined as the ratio of additional margin loss over DCD. Based on peak distortion analysis and statistical jitter modeling methodology, a general formula is derived to calculate data channel DCD amplification. Simulation results confirm the theory and show that data channel DCD amplification also scales with channel loss but at a lower rate than the clock channel DCD.

#### REFERENCE

- S. Chaudhuri, W. Anderson, J. Bryan, J. McCall, and S. Dabrai, "Jitter amplification characterization of passive clock channels at 6.4 and 9.6 Gb/s," Proc. IEEE 15th Topical Meeting on Electrical Performance of Electronic Packaging, Scottsdale, AZ, Oct. 2006, pp. 21-24.

- [2] C. Madden, S. Chang, D. Oh and C. Yuan, "Jitter amplification considerations for PCB clock channel design," Proc. IEEE 16th Topical Meeting on Electrical. Performance Electronic Packaging, Atlanta, GA, Oct. 2007, pp. 135-138.

- [3] S. Chang, D.Oh, and C. Madden, "Jitter modeling in statistical link simulation," IEEE International Symposium on Electromagnetic Compatibility, Detroit, MI, Aug. 2008, pp. 1-4.

- [4] F. Rao and S. Hindi, "Frequency domain analysis of jitter amplification in clock channel," Proc. IEEE 21th Topical Meeting on Electrical Performance of Electronic Packaging, Tempe, AZ, Oct. 2012, pp. 51-54.

- [5] D. Oh, F. Lambrecht, S. Chang, Q. Lin, J. Ren, C. Yuan, J. Zerbe, and V. Sto-janovic, "Accurate system voltage and timing margin simulation in high-speed I/O system design" IEEE Transaction on Advanced Packaging, vol. 31,no. 4, pp. 722-730, Nov. 2008.

- [6] B. K. Casper, M. Haycok, and R. Mooney, "An accurate and efficient analysis method

- for multi-Gb/s chip-to-chip signaling schemes," IEEE Symposium on VLSI Circuits, June 2002, pp. 54-57.

- [7] J.Ren, D.Oh, "Multiple edge responses for fast and accurate syestem simulations," IEEE transactions on Advanced Packageing, vol.31,no.4,pp.741-748. Nov.2008

- [8] V.Stojanovic, M.Horowitz, "Modeling and Analysis of High-Speed Links, IEEE Custom Integrated Circuits Conference, September 2003.

- [9] J. Caroselli and C. Liu, "An analytic system model for high speed interconnects and its application to the specification of signaling and equalization architectures for 10Gbps backplane communication," DesignCon, February 2006.

# CHAPTER 3. ACCURATE JITTER DECOMPOSITION IN HIGH-SPEED LINKS

In a high-speed digital communication system, jitter performance plays a crucial role in Bit-Error Rate (BER). It is important to accurately derive each type of jitter as well as total jitter (TJ) and to identify the root causes of jitter by jitter decomposition. In this chatper, a jitter decomposition algorithm using least squares (LS) is proposed, which simultaneously separates inter-symbol interference (ISI), random jitter (RJ) and periodic jitter (PJ). This algorithm includes a new time domain ISI model, which is more effective than the conventional cursor convolution techniques. The new proposed algorithm only requires the time invariant condition, which is true for almost all systems, while the traditional ISI model is valid only with the linear time invariant assumption. Compared to conventional methods, the proposed jitter decomposition method is able to obtain the estimated individual jitter component values with fine accuracy by using fewer samples of total jitter data. The efficiency and accuracy of the proposed method are demonstrated by simulation and hardware experiments.

#### 3.1 Introduction

With the ever-increasing demand of high speed data rate in serial communication systems, jitter becomes a dominant factor affecting system performance and the bit-error-rate (BER). As it also limits timing margin for the system today, accurate jitter analysis is crucial for next-generation I/O design in order to obtain an acceptable BER.

Jitter is defined as the deviation of transition edges from their ideal location in time and contains multiple components each with different characteristics. The total jitter (TJ) in data signal consists of deterministic jitter (DJ) and random Jitter (RJ). RJ follows unbounded Gaussian distribution due to noise sources (such as thermal noise, flick noise, shot noise etc). DJ obeys bounded distribution and can be decomposed into periodic jitter (PJ) and data dependent jitter (DDJ), bounded uncorrelated Jitter (BUJ). PJ comes from external deterministic noise sources coupling into a system, such as switching power supply noises. DDJ is further divided into duty cycle distortion (DCD) and inter-symbol Interference (ISI). Non-idealities, such as asymmetric rising and falling edges of the clock path generate DCD which the duration of logical 1 is different from the duration of a logical 0. ISI is caused by the bandwidth limitation, loss and reflection of the channel. DDJ is related to the bit sequence.

Understanding the amount of jitter introduced by each jitter source is imperative for predicting overall system performance [1]. Jitter decomposition is a key tool used in such scenarios to identify the root causes of jitter. Jitter can be measured using different methods either using external instrument (oscilloscope, spectrum analyzer and time interval analyzer (TIA)) or on-chip circuit jitter measurement. However, these on-chip jitter measurement circuits [2-6] require a large amount of die area if the jitter histograms have to be collected in real-time. Different off-chip decomposition approaches have been developed in the past. Generally, there are three popular category approaches to decompose jitter: 1) the ones based on histogram or statistical methods; 2) the ones with frequency-domain based analysis; and 3) the ones with time-domain based analysis relying on jitter measurements carried out in real-time.

The histogram methods are based on the popular Gaussian tail model [1] by using the probability distribution of collected jitter values. For example, RJ could be observed at the outer tails of a TJ distribution. Thus, this type of method is also referred to as a tail fitting algorithm. Researchers reported various methods to separate RJ and DJ

components with different tail fitting algorithms [7-9]. However, a large amount of jitter samples is required to correctly identify the fit tail part of distribution. Deconvolution methods [10] rely on the idea that in histogram based analysis, a TJ probability density function (PDF) is given as convolution result of the RJ and DJ components. If one of these two components is approximately estimated, one can use a deconvolution algorithm to determine other components, and thus to retrieve the Gaussian model parameters. However, a major drawback of these methods is that they suffer from lack of accuracy because either the DJ or RJ component has to be estimated prior to the deconvolution.

For the frequency-based method, the time-domain series of jitter can also be represented and analyzed in the frequency domain using the Fourier transform (FT) [11-14]. Then, researchers can use the power spectral density (PSD) to represent the jitter spectrum by applying averaging techniques. Correspondingly, peaks in the spectrum can be interpreted as PJ or DDJ, while the average noise floor denotes the power of RJ. However, they used a clock pattern to estimate the RJ and PJ in the system and the ISI cannot be derived from long run-length patterns. Jitter analysis techniques based on time-domain [15-17] rely on jitter measurements carried out in a real-time mode. This is only possible to those dedicated real-time measurement systems, such as high-speed sampling scopes or TIA. Those instruments also include the histogram or spectral test methods. Unfortunately, histogram, spectral and time-domain methods need sufficient memory depth to acquire enough data so that the accuracy can be assured through these digital signal processing (DSP) techniques [18]. In [19], a low-cost jitter separation method based on ADC testing was developed. However, this method is limited to separate jitter in only clock channel with low speeds.

One important jitter component needed to be addressed is ISI jitter. The ISI jitter plays an important part in the TJ. The ISI modelling methods have been introduced in the past. In [12, 20], they modelled the channel as a first-order and a second-order low-pass filter. However, in presence of discontinuities, such a model is too simple to

represent the real channel and becomes invalid. In [21], the ISI modelling is commonly based on the convolution technique. However, it is very time consuming since the cursor is usually 100-bit long.

In this chapter, we present a jitter decomposition algorithm based on LS which has advantages of 1) accurate estimation for PJ, ISI and RJ; 2) fewer data samples than the instrument test which saves the memory requirement; and 3) the new ISI modelling is accurate and efficient to ISI jitter estimation. In this decomposition algorithm, the ISI jitter model in time domain is simpler than the conventional ISI cursors convolution technique. Another advantage of the proposed ISI modelling is its being more accurate and realistic than the low pass filter model. The PJ and RJ were also modelled by a traditional method [1]. The LS was used to obtain parameter values in the above-mentioned jitter model [22-23]. Compared with the simulation and conventional instrument test methods, the proposed method shows great accuracy in the jitter decomposition.

The rest of the chapter is organized as follows: In Section II, the conventional PJ, RJ models are reviewed and the new ISI jitter model is presented. In Section III, the TJ model is introduced. A LS method is applied to the TJ model and the estimation of jitter component is derived. In Section IV, the validation for the ISI model and jitter decomposition simulation results are presented. In Section V, the hardware experiment is presented. Section VI concludes the chapter.

# 3.2 Jitter Modeling

This section presents PJ, RJ and ISI jitter models considered in the algorithm. PJ and RJ models are widely used in popular jitter analysis. We developed a new time domain ISI jitter model for a lossy channel which is efficient at ISI estimation.

#### 3.2.1 Periodic Jitter(PJ)

PJ is a repeating jitter signal at certain frequencies. It is typically derived from the noise in a switching power supply or caused by PLL reference clock feedthrough. The mathematical model of PJ [1] is

$$\triangle t_{PJ}[n] = A\sin(2\pi f_0(t - nT) + \emptyset) = a\sin\left(\frac{2\pi f_0 n}{f_s}\right) + b\cos\left(\frac{2\pi f_0 n}{f_s}\right)$$

(3.1)

where  $\triangle t_{PJ}[n]$  is a jitter amount at sampling time nT; A is the amplitude of PJ;  $f_0$  is the frequency of PJ. In a real system, it can be input reference clock of PLL or power supply noise and extracted from the data through spectral analysis. In this chapter, we consider the PJ from reference clock as an example;  $f_s$  is frequency of data stream, and  $\phi$  is the phase.

In equation 3.1, a and b are the estimation parameters for PJ in the algorithm.

#### 3.2.2 Random Jitter (RJ)

RJ is caused by unbounded jitter sources, such as thermal noise, flick noise, and shot noise which can be modeled as Gaussian white noise. Gaussian jitter PDF is defined as

$$f_{RJ}(\Delta t) = \frac{1}{\sqrt{2\pi\sigma}} \exp{-\frac{(\Delta t - \mu)^2}{2\sigma^2}}$$

(3.2)

In equation 3.2,  $\mu$  is the mean and  $\sigma$  is the standard deviation of Gaussian distribution. In this model, the  $\mu$  is zero and  $\sigma$  is the estimation parameter for RJ in the algorithm.

#### 3.2.3 Inter-Symbol Interference Jitter (ISIJ)

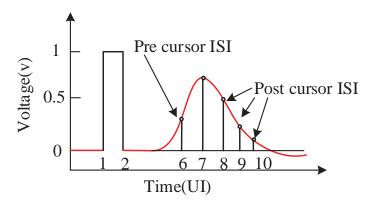

ISI is caused by reflections and loss in a channel. Figure 3.1 shows a single-bit response after a lossy channel. The pulse becomes widened and attenuated, and it occupies the pre-cursor and post cursor samples. Traditionally, ISI cursors convolution technique is used in ISI modeling. However, this process is time-consuming when the number of

Figure 3.1 The pulse response of the channel

cursor is large. For instance, typical single-bit responses are often more than 100bit long [21]. This convolution approach fails when the non-linearity of the system is severe, or when the data pattern is non-white.

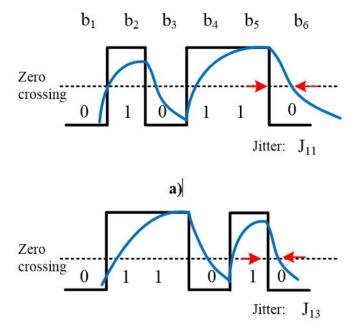

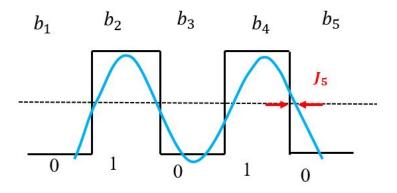

Since sophisticated methods, like transmitter finite impulse response (TX-FIR) equalizer, are needed to properly equalize to the precursor, we consider the k-bit post cursor has a dominant effect on ISI. We use an example to illustrate the time domain ISI model. Considering the data sequence b1-b6 as shown in Figure 3.2, the black curve is the ideal data sequence and blue curve is the actual data sequence due to ISI. b6 is the current bit, b1-b5 are preceding five bits (5 bits post cursor). b1-b5 has 32 binary combinations. If b1-b5 is 01011 as shown in Figure 3.2(a), the time deviation of actual b6 edge and the ideal b6 edge is defined as ISI induced jitter  $J_{11}$ . The index 11 is the decimal representation of 01011. If b1-b5 is 01101 shown in Figure 3.2(b), the time deviation of actual b6 edge and the ideal b6 edge is thus noted as jitter  $J_{13}$ . The index 13 is the decimal representation of 01101. Different b1-b5 binary combinations generate different ISI jitter amount to current bit b6. Table 3.1 describes the ISI model parameters which include binary combinations, a corresponding jitter J and a sign C. In this example, the

5-bit post cursor has 32 binary combinations and each binary combination generates a corresponding jitter value J. The corresponding sign C is used to represent which kind of binary combination of 5-bit post cursor is selected. In Figure 3.2(a), the 5-bit binary combination is 01011 and the corresponding jitter value is  $J_{11}$ , the corresponding sign  $C_{11}$  is equal to 1 while other corresponding signs are all zeros.

Table 3.1 The parameters of ISI model

| b1-b5 binary combinations | Corresponding Jitter | Corresponding sign |

|---------------------------|----------------------|--------------------|

| 00000                     | $J_0$                | $C_0$              |

|                           | • • •                | •••                |

| 01011                     | $J_{11}$             | $C_{11}$           |

|                           | •••                  | • • •              |

| 11111                     | $J_31$               | $C_{31}$           |

Figure 3.2 An example of ISI modeling

Based on the observation that different post cursor binary combinations generate different ISI jitter amounts on the current bit, we can use a formula to describe the ISI jitter model. The equation is given by

$$\triangle t_{ISI}[n] = \sum_{0}^{2^{K}-1} J_l \times C_l[n]$$

(3.3)

$$C_{l} = \begin{cases} 1, \text{ if binary to decimal } b_{(n-k)} b_{(n-k+1)} \cdots b_{(n-1)} == l \\ 0, \text{ otherwise} \end{cases}$$

(3.4)

where  $\triangle t_{ISI}[n]$  is ISI jitter of data bit n at sample time nT. The jitter of current bit  $b_n$  is determined by binary combinations of previous k bits from  $b_{n-k}$  to  $b_{n-1}$ . l is the decimal number of binary combination  $b_{(n-k)}b_{(n-k+1)}\cdots b_{(n-1)}$ .  $J_l$  is the jitter value of the lth binary combination to the current bit  $b_n$ .  $C_l$  is a corresponding sign which represents the binary combination of the previous k-bit. The equation describes that ISI jitter of the current  $b_n$  is the jitter amount of the previous k-bit. This model does not assume any linearity or superposition requirements on the ISI jitter as a function of the previous k-bit, nor does it rely on linearity in the conversion from data waveform voltage errors to timing errors near zero crossing, thus making the ISI model more robust to channel non-idealities.  $J_l$  is the estimation parameter in the algorithm.

The post cursor number k can be obtained from the channel pulse response given the threshold voltage as shown in Figure 3.1

# 3.3 Jitter Decomposition Algorithm

In this section, we present the TJ modelling used in this study, and then explain the details of the decomposition algorithm.

#### 3.3.1 Total Jitter

The TJ in time domain is considered as the linear sum of DJ components and the square root of the RJ components [21]. With the proposed ISI jitter modelling, the TJ

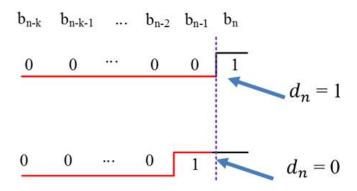

Figure 3.3 Data transition sign  $d_n$

in bit n with PJ, RJ and ISI can be simulated as:

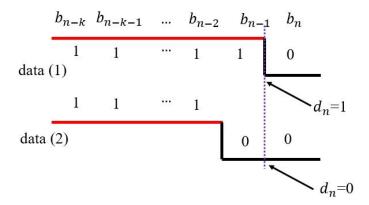

$$x[n] = d_n \times [\triangle t_{PJ}[n] + \triangle t_{ISI}[n] + \triangle t_{RJ}[n]]$$

(3.5)

where x[n] is the TIE amount at sampling time nT.  $d_n$  is data transition sign used to indicate the existence of a 0 to 1 or 1 to 0 transition from bit n-1 to bit n.  $d_n$  is 1 only when there is a falling or rising edge from bit n-1 to bit n as shown in data (1) of Figure 3.3  $d_n$  is 0 when there is no data transition from bit n-1 to bit n as shown in data (2) of Figure 3.3 When  $d_n$  is 0, no jitter exists for the current bit n.

#### 3.3.2 Jitter decomposition by Least Squares (LS)

In order to estimate the parameters in the proposed model, a LS based decomposition method is proposed. Equation (4) shows that TJ is a linear equation. For a linear time invariant system, LS estimation overcomes the convergence problem [22-23] and does not require any special distribution properties for the input. Based on this, we applied the LS to estimate the PJ, RJ, and ISI parameters  $[a, b, J_0, J_1, \dots, J_{(2^k-1)}]$ .

Define that M bits absolute TIE sequence is shown in Figure 3.4 The absolute TIE in each bit is  $x[1], x[2], \dots, x[M]$  taken at sampling time  $1T, 2T, \dots, MT$ , respectively.

Figure 3.4 M bits total jitter sequence

Then the absolute TIE sequence  $Z_M$  can be expressed by the following equation [21]

$$Z_{M} = \begin{bmatrix} x(1) \\ x(2) \\ \vdots \\ x(M) \end{bmatrix} = H_{M}\theta + V_{M}$$

$$(3.6)$$

where  $V_M$  is RJ vector (denoted as  $[[1], [2], cdots, [M]]^T$ ) for the TIE sequence, representing  $[a, b, J_0, J_1, \dots, J_{(2^k-1)}]^T$  is the estimation parameters for PJ, DCD and ISI.  $H_M$  is the coefficient matrix for the whole jitter sequence.  $H_M$  is the coefficient matrix for the whole jitter sequence. The submatrix A in  $H_M$  is PJ coefficients matrix and submatrix B is ISI coefficients matrix.

$$H_{M} = \begin{bmatrix} A & B \end{bmatrix} A = \begin{bmatrix} d_{1} \sin\left(\frac{2\pi f_{0}}{f_{s}}\right) & d_{1} \cos\left(\frac{2\pi f_{0}}{f_{s}}\right) \\ \vdots & \ddots & \vdots \\ d_{M} \sin\left(\frac{2\pi f_{0}M}{f_{s}}\right) & d_{M} \cos\left(\frac{2\pi f_{0}M}{f_{s}}\right) \end{bmatrix} B = \begin{bmatrix} d_{1}C_{01} & \cdots & d_{1}C_{2^{k}-11} \\ d_{2}C_{02} & \cdots & d_{2}C_{2^{k}-12} \\ \vdots & \ddots & \vdots \\ d_{M}C_{0M} & \cdots & d_{M}C_{2^{k}-1M} \end{bmatrix}$$

$$(3.7)$$

In equation 3.7,  $C_{li}$  can be extracted from the data stream and store in look up table. For instance, if binary combination of post-cursor of the ith bit data stream is 01101, then  $C_{12i}$  is 1 and other  $C_{xi}$  is 0. Since the PJ frequency  $f_0$  can be obtained from spectral analysis, we assume the  $f_0$  is a known parameter in this chapter.  $f_s$  is the data rate.

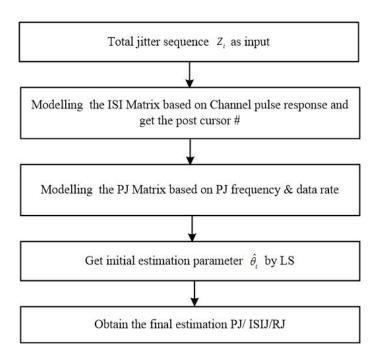

Figure 3.5 The flow chart of proposed algorithm

The solution  $\widehat{\theta}_M$  for length of absolute TIE M bits is

$$\widehat{\theta} = \left[ H_M^T H_M \right]^{-1} H_M^T Z_M \tag{3.8}$$

The estimation parameter  $\widehat{\theta}_M$  is

$$\widehat{\theta} = \left[ \widehat{a}, \widehat{b}, \widehat{J}_0, \widehat{J}_1, \cdots, \widehat{J}_{2^K - 1} \right]$$

(3.9)

The amplitude of estimation PJ is

$$\widehat{A} = \sqrt{\widehat{a}^2 + \widehat{b}^2} \tag{3.10}$$

The ISI is calculated by

$$\widehat{ISI}_{pk-pk} = \max(\widehat{J}_0, \widehat{J}_1, \cdots, \widehat{J}_{2^{K}-1}) - \min(\widehat{J}_0, \widehat{J}_1, \cdots, \widehat{J}_{2^{K}-1})$$

(3.11)

The variance of RJ is

$$\sigma^2 = var(Z_M - H_M \widehat{\theta}) \tag{3.12}$$

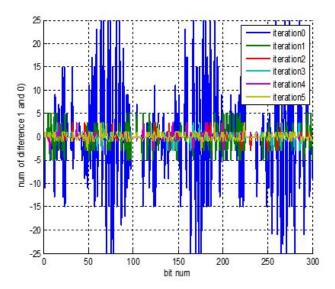

The flow chart of the proposed algorithm is given in Figure 3.5. The jitter sequence with PJ, ISI, and RJ is the input of the algorithm. The ISI matrix is formed based on data stream information and the PJ matrix is formed based on the data rate and PJ frequency (from the spectral analysis). According to equation 3.8, the initial estimation jitter component value  $\hat{\theta}$  could be obtained by LS. The final estimation of PJ, ISI, and RJ values is based on equation 3.10 3.11 and 3.12 respectively.

#### 3.4 Simulation Results

In this section, the proposed decomposition methods are validated by Matlab simulation. PRBS-7 data length is 1.27k bits and the data rate are 10Gb/s and 25Gb/s in the simulation respectively. The PJ was a sine wave with 100MHz frequency at 10Gb/s and 250MHz frequency at 25 Gb/s.

#### 3.4.1 Validation of the ISI Jitter Estimation

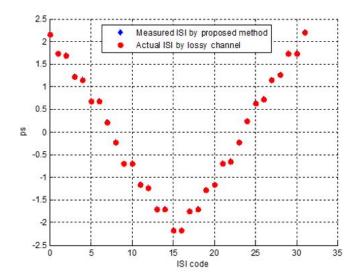

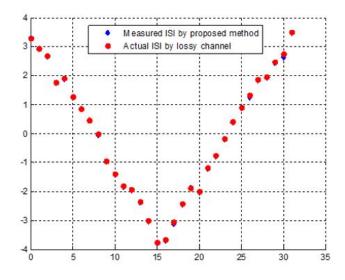

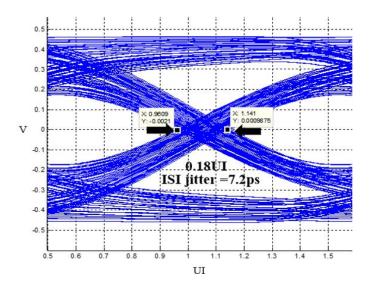

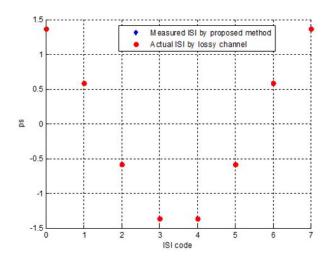

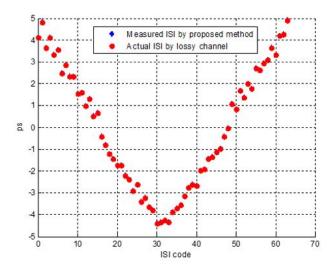

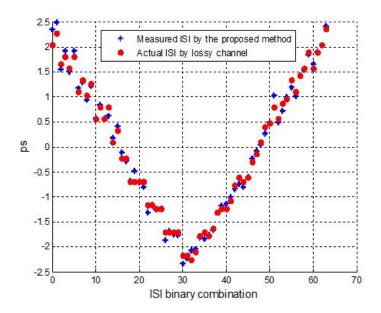

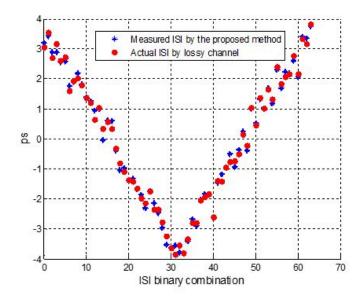

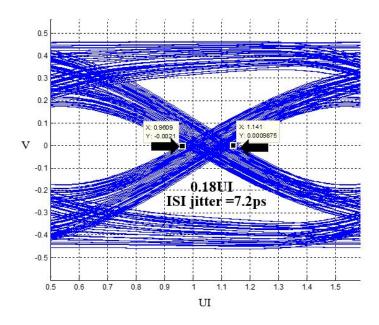

In order to verify that the ISI jitter estimation is previous k-bit dependent, we used ISI TIE jitter sequence as reference criteria. The extraction of S-parameter of a PCB transmission line (channel A) with insertion loss 3.5dB at 5GHz and 7.5dB at 12.5GHz was used to generate the ISI TIE sequence. We classified the ISI jitter sequence to  $2^k$  binary combinations. The post cursor number k of the transmission line is 5, which was obtained from the channel pulse response. These 5 bits post cursors have 32 binary combinations from 00000 to 11111. The corresponding jitter amount are from  $J_0$  to  $J_{31}$ . The red dots in Figure 3.6 and Figure 3.7 represents the TIE ISI jitter in each ISI binary combination which shows that different binary combinations correspond to different ISI jitter at 10Gb/s and 25Gb/s respectively. The eye diagram of PRBS 7 only with ISI in Figure 3.8 shows ISI jitter (pk-pk) in this transmission line is about 7.2 ps at 25Gb/s.

Figure 3.6 Comparison of ISI TIE binary combination and estimation result for 10Gb/s

Figure 3.7 Comparison of true and estimation ISI for 25Gb/s

In order to verify the decomposition algorithm, the whole PRBS7 data stream with only ISI jitter was sent to the proposed method.

Figure 3.8 Eye diagram of PRBS-7 only with ISI at 25Gb/s

Figure 3.9 Comparison of true and estimation ISI for Channel B at 10Gb/s

The estimated ISI jitter for each binary combination is represented by blue dots in Figure 3.6 for 10Gb/s and in Figure 3.7(a) for 25Gb/s. They show that the estimated ISI and actual ISI are very close both at 10Gb/s and 25Gb/s. The estimated ISI (pk-pk) value is about 4.6 ps at 10Gb/s and 7.2 ps at 25Gb/s which is very close to the pk-pk

Figure 3.10 Comparison of true and estimation ISI for Channel C at 10Gb/s

jitter obtained from the eye diagram in Figure 3.8.

We also modeled channel B with 3dB loss and channel C with 5dB loss at 5GHz to verify the proposed ISI model. The simulation results are shown in Figure 3.9 and 3.10, and mathes the true ISI well.

#### 3.4.2 Validation of PJ, DCD and ISI Jitter

In the 10Gb/s simulation, PRBS-7 data stream were generated by Matlab Simulink toolbox with different PJ (0ps, 20ps pk-pk), RJ (0ps, 2.13ps, rms value) and ISI jitter caused by channel A (4.6 ps, pk-pk) was sent to the algorithm. The simulation results are summarized in the third column group of Table 3.2. It shows the estimated jitter is very close to the added jitter.

In the 25Gb/s simulation, PRBS-7 data stream with different jitter component were generated. The data stream with different PJ (0,1.5ps, 4ps, 8ps peak-peak value), RJ (0,2.13 ps) and ISI jitter caused by channel A (7.2ps, pk-pk value) was sent to the algorithm. The simulation results are summarized in Table 3.3. The estimation error of ISI is less than 0.5 ps. The estimation error of PJ is close to 0 ps. DCD estimation were

larger than the added caused by the jitter amplification due to channel loss.

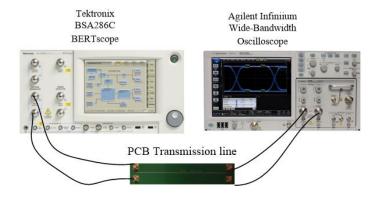

#### 3.5 Measurement Results

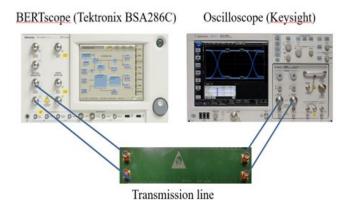

To verify the ISI (pk-pk) estimation and the accuracy and efficiency of the algorithm, a hardware test bench was used (shown in Figure 3.11) to measure the jitter components for 10Gb/s. A Tektronix BSA286C BERTscope was used to generate data stream with PJ. An Agilent Infiniium Wide-Bandwidth Oscilloscope was used to measure the jitter with internal software. The same PCB transmission line in simulation part A was used to generate the ISI jitter. All experiments were done at a data rate of 10Gb/s.

We also used the result of JNEye with conventional decomposition algorithms as reference to compare the proposed method. JNEye is Intels state-of-the art jitter and noise link analysis tool for evaluate high-speed serial link performance. The jitter decomposition of this platform is based on hybrid algorithms with statistical, frequency-domain, and time-domain analysis with dedicated jitter components modeling and extraction. The accuracy of JNEye has been validated with both simulation and measurement correlations [22]. All tests for comparison were done at 10Gb/s and 25Gb/s.

Figure 3.11 The 10Gb/s experimental test bench

#### 3.5.1 Validation of the ISI Jitter pk-pk Estimation

Since the ISI jitter (pk-pk) generated by the PCB transmission line (channel A) is unknown, the ISI measurement result of the oscilloscope is as a reference. In the experiment, jitter free PRBS7 data generated by BERTscope was sent to the PCB transmission line and the output of transmission line was connected to oscilloscope to obtain the ISI jitter value.

In the proposed method, the PRBS-7 data stream with ISI jitter was sent to the algorithm and the estimation ISI value was obtained. The channel A was used in JNEye to generate PRBS-7 with ISI and then decompose the ISI jitter. The comparison is listed in the Table 3.2. In the added jitter term, the unknown for ISI means that the ISI jitter amount is unknown when the transmission line is added. The ISI value in the measurement is 5.1 ps and the estimation in JNEye is 4.4ps. The one in the proposed method is 4.6 ps. All values are very close. Therefore, the ISI modeling is validated. PJ in the proposed method is 0ps (pk-pk) while the oscilloscope result is about 1.4ps. RJ (rms value) in the simulation is 0ps while the one in the measurement is 1.4ps due to the instrument noise.

#### 3.5.2 Comparison of the Accuracy and the Sample Data

In the hardware experiment, PRBS-7 data stream at 10Gb/s with different PJ (0ps and 20ps pk-pk) generated by BERTscope was sent to channel A and then sent to oscilloscope. PRBS7 data stream with different amounts of PJ and ISI jitter were sent to the proposed method and JNEye.

Table 3.2 shows the comparison results among oscilloscope, JNEye and the proposed method. When the measurement result is stable, the experiment should run several minutes according to test experience. When the added ISI is 0, the oscilloscope result of ISI jitter is about 3.2 ps due to the cable while in the proposed algorithm the estimation is about 0 ps. The DCD measurement result is 0.8ps while in the proposed method is 0.

The data sample in each simulation is 8k, but the oscilloscope requires at least 200k data in the experiment. Therefore, the proposed algorithm has comparable accuracy using fewer data samples than instrument and have the same accuracy compare to JNEye.

Table 3.2 Comparasion the proposed method, instrument and JNeye at 10Gb/s unit (ps)

| Added<br>jitter |    |         | Instrument |      |     | JNeye |      |     | The propose method |      |     |

|-----------------|----|---------|------------|------|-----|-------|------|-----|--------------------|------|-----|

| RJ              | PJ | ISI     | RJ         | PJ   | ISI | RJ    | PJ   | ISI | RJ                 | PJ   | ISI |

| 0               | 0  | unknown | 1.5        | 1.4  | 5.1 | 0     | 0    | 4.4 | 0                  | 0.07 | 4.6 |

| 0               | 20 | 0       | 1.4        | 20.5 | 3.2 | 0     | 20.1 | 4.4 | 0                  | 20.2 | 4.7 |

| 2.13            | 20 | unknown | 2.49       | 20.3 | 6.5 | 2.2   | 20   | 4.4 | 2.14               | 20.1 | 4.6 |

Table 3.3 Comparasion the proposed method and JNeye at 25Gb/s unit (ps)

| Added<br>jitter |    |         | JNeye       |     |      |     |             |      | The propose method |     |  |

|-----------------|----|---------|-------------|-----|------|-----|-------------|------|--------------------|-----|--|

| RJ              | РJ | ISI     | sample data | RJ  | PJ   | ISI | sample data | RJ   | PJ                 | ISI |  |

| 0               | 0  | unknown | 8k          | 0   | 0    | 4.4 | 1.27k       | 0    | 0.07               | 4.6 |  |

| 0               | 20 | unknown | 8k          | 0   | 20.1 | 4.4 | 1.27k       | 0    | 20.2               | 4.7 |  |

| 2.13            | 20 | unknown | 8k          | 2.1 | 20   | 4.4 | 1.27k       | 2.12 | 20.1               | 5.2 |  |

| 2.13            | 20 | 0       | 8k          | 2.2 | 19.8 | 0   | 1.27k       | 2.1  | 20.4               | 0   |  |

It shows that both of two methods have the same estimation accuracy with the same sample data at 10Gb/s. For the 25Gb/s comparison, PRBS7 data stream with different PJ (1.5ps,4ps,8ps pk-pk), RJ (0ps,2.13ps) and ISI jitter generated from channel A were sent to JNEye and the proposed method.

Table 3.3 shows the estimation results in the proposed method and the JNEye estimation result. Both of two methods have the same estimation accuracy with the same sample data. However, the proposed method has two obvious advantages. First, the proposed method was used less sample data than instrument test or commercial simulation platform. Second, the proposed method can provide ISI analysis in detail for each ISI binary combination.

#### 3.6 Conclusion

An efficient and accurate algorithm that simultaneously extracts the periodic jitter, random jitter and ISI jitter is presented. This method is based on time-domain ISI modelling which is simpler than the conventional cursor convolution technique. It utilizes fewer sample data while maintaining great estimation accuracy in both clock pattern and data pattern. The comparison between simulation results and the hardware test ones demonstrates the accuracy of the proposed jitter measurement method. However, there are still limitations in the proposed method. It is only applied in low lossy channels, which means the eye diagram should be open before the receiver of system and the data logic value can be correctly determined. The algorithm needs the TJ sequences as an input which requires extra instruments such as TIA to store the jitter sequence.

#### 3.7 Acknowledge

The authors would like to thank Huawei Technologies Co. Ltd for providing the PCB board and instruments for hardware validation and Intel for providing JNeye validation in this chapter.

#### Reference

- [1] M. P. Li, "Jitter, noise and signal integrity at high-speed," Prentice Hall Pearson Education, 2007, Chapter 6, pp.163-185.

- [2] K.-H. Cheng, J.-C. Liu, C.-Y. Chang, S.-Y. Jiang, and K.-W. Hong, "Built-in jitter measurement circuit with calibration techniques for a 3-GHz Clock Generator," IEEE Trans. VLSI Systems, vol. PP, no. 99, pp. 111, Jun. 2010.

- [3] J.-C. Hsu and C. Su, "BIST for measuring clock jitter of charge-pump phase-locked loops," IEEE Trans. Instrumentation and Measurement, vol. 57, no. 2, pp. 276285, Feb. 2008.

- [4] K. Ichiyama, M. Ishida, T. J. Yamaguchi, and M. Soma, "Novel CMOS circuits to measure data-dependent jitter, random jitter, and sinusoidal jitter in real time," IEEE Trans. Microw. Theory Tech., vol. 56, no. 5, pp. 12781285, May 2008.

- [5] S.-Y. Jiang, K.-H. Cheng, and P.-Y. Jian, "A 2.5-GHz built-in jitter measurement system in a serial-link transceiver," IEEE Trans. VLSI Systems, vol. 17, no. 12, pp. 1698 1708, Dec. 2009.

- [6] K. Nose, M. Kajita, and M. Mizuno, "A 1-ps resolution jitter-measurement macro using interpolated jitter oversampling," IEEE J. Solid-State Circuits, vol. 41, no. 12, pp. 29112920, Dec. 2006.

- [7] M. Li, J. Wilstrup, R. Jessen, and D. Petrich, "A new method for jitter decompo-

- sition through its distribution tail fitting," in Proc. International Test Conference. IEEE, Sept. 1999, pp. 788794.

- [8] G. Hnsel, K. Stieglbauer, G. Schulze, and J. Moreira, "Implementation of an economic jitter compliance test for a multi-gigabit device on ATE," IEEE Int. Test Conf. (ITC04), pp. 13031312, Oct. 2004.

- [9] D. Hong and K.-T. Cheng, "An accurate jitter estimation technique for efficient high speed I/O Testing," IEEE Asian Test Symp. (ATS07), pp. 224229, Oct. 2007.

- [10] R. Stephens, "Separation of random and deterministic components of jitter," U.S. Patent 7 149 638, Dec. 12, 2006.

- [11] C.-K. Ong, D. Hong, K.-T. Cheng, and L.-C. Wang, "Jitter spectral extraction for multi-gigahertz signal," in Proc. ASP-DAC, Asia and South Pacific. IEEE, Jan. 2004, pp. 298–303.

- [12] V.K Sharma, J.N. Tripath, R. Nagpal, S. Deb and R. Malik, "A Comparative analysis of jitter estimation techniques," in proc.IEEE International Conference on Electronics, communication and computational engineering (ICECCE), 2014

- [13] H. Pang, J. Zhu, and W. Huang, "Jitter decomposition by fast Fourier transform and time lag correlation," in IEEE Int. Conf. Communications, Circuits and Systems ICCCAS, Jul. 2009, pp. 365368.

- [14] T. Yamaguchi, H. Hou, K. Takayama, D. Armstrong, M. Ishida et al., "An FFT-based jitter separation method for high-frequency jitter testing with a 10x reduction in test time," IEEE Int. Test Conf. (ITC07), pp. 18, Oct. 2007.

- [15] Q. Dou and J. Abraham, "Jitter decomposition by time lag correlation, aration method for high-frequency jitter testing with a 10x reduction in test time," IEEE Int. Symp. Quality Electronic Design (ISQED06), Mar. 2006.

- [16] J. Zhu and W. Huang, "Jitter analysis and decomposition based on EMD/HHT in high-speed serial communications," in Proc. of IEEE Int. Conf. Testing and Diagnosis (ICTD09), Apr. 2009, pp. 14.

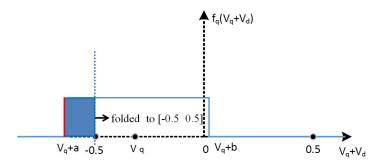

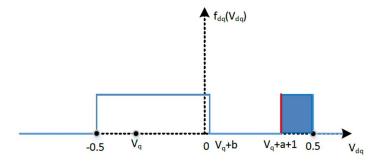

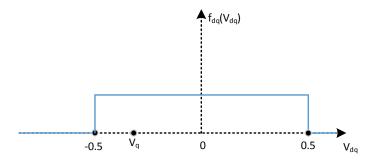

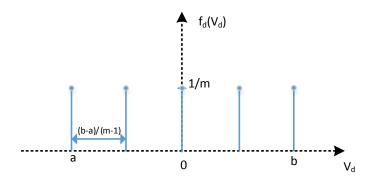

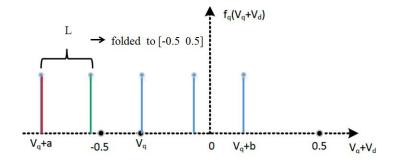

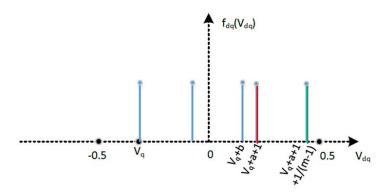

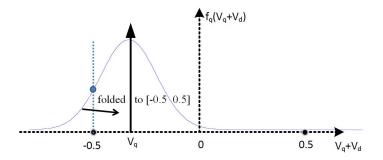

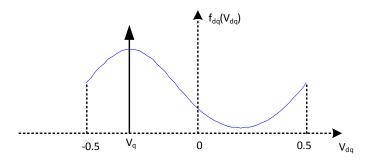

- [17] K. Bidaj, J.Baptiste and J.Deroo, "Time-domain PLL modeling and RJ/DJ jitter decomposition," in Proc. of IEEE, 22-25 May 2016